# Application Note UFS Memory Device JEDEC UFS Ver.2.0 Revision 0.1 (Mar., 2014) TOSHIBA Corporation

# Disclaimer

- The information contained herein is presented only as a guide for the application of TOSHIBA products. No responsibility is assumed by TOSHIBA for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of TOSHIBA or others.

- The information in this document is provided "as is", with no warranties.

- This document is provided for informational purpose only.

- The information in this document is preliminary and is subject to change at any time, without prior notice.

# About this document

This document is intended to provide information for the use of TOSHIBA UFS memory devices. The information given in this document will help the user to understand how to use it and the boot process based upon the JEDEC UFS standard versions 2.0.

# TABLE OF CONTENTS

| 1.                                                                                                                      | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 8                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| 1.1                                                                                                                     | OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8                                                                                                  |

| 1.2                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                    |

| 1.3                                                                                                                     | NORMATIVE REFERENCE                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 9                                                                                                  |

| 2.                                                                                                                      | UFS SYSTEM ARCHITECTURE                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 10                                                                                                 |

| 2.1                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                    |

| 2.2                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                    |

| 2.3                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                    |

| 2.4<br>2.5                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                    |

| 2.5<br>2.6                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                    |

|                                                                                                                         | INITIALIZATION SEQUENCE                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                    |

|                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                    |

| 3.1<br>3.2                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                    |

| 3.3                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                    |

| 3.4                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                    |

| 4.                                                                                                                      | DEVICE CONFIGURATION                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 20                                                                                                 |

| 4.1                                                                                                                     | . LOGICAL UNIT CONFIGURATION                                                                                                                                                                                                                                                                                                                                                                                                                                              | 20                                                                                                 |

| 4.2                                                                                                                     | BOOT W-LU CONFIGURATION                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 23                                                                                                 |

| 4.3                                                                                                                     | . REFERENCE CLOCK CONFIGURATION                                                                                                                                                                                                                                                                                                                                                                                                                                           | 26                                                                                                 |

| 5.                                                                                                                      | POWER MODE CONTROL                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 27                                                                                                 |

| - 1                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 27                                                                                                 |

| 5.1                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                    |

| 5.2                                                                                                                     | UFS POWER MODE CONTROL                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 29                                                                                                 |

|                                                                                                                         | UFS POWER MODE CONTROL                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 29                                                                                                 |

| 5.2<br>5.3                                                                                                              | 2. UFS POWER MODE CONTROL<br>5. AUTO SLEEP FEATURE                                                                                                                                                                                                                                                                                                                                                                                                                        | 29<br>31<br>32                                                                                     |

| 5.2<br>5.3<br><b>6.</b> 1                                                                                               | <ul> <li>UFS POWER MODE CONTROL</li> <li>AUTO SLEEP FEATURE</li> <li>RESET OPERATION</li> <li>POWER-ON RESET</li> </ul>                                                                                                                                                                                                                                                                                                                                                   | 29<br>31<br><b>32</b><br>32                                                                        |

| 5.2<br>5.3<br><b>6.</b> 1<br>6.1<br>6.2                                                                                 | <ul> <li>UFS POWER MODE CONTROL</li> <li>AUTO SLEEP FEATURE</li> <li><b>RESET OPERATION</b></li> <li>POWER-ON RESET</li> <li>HARDWARE RESET</li> </ul>                                                                                                                                                                                                                                                                                                                    | 29<br>31<br>32<br>32<br>33                                                                         |

| 5.2<br>5.3<br><b>6.</b> 1<br>6.1<br>6.2<br>6.3                                                                          | <ul> <li>UFS POWER MODE CONTROL</li> <li>AUTO SLEEP FEATURE</li> <li><b>RESET OPERATION</b></li> <li>POWER-ON RESET</li> <li>HARDWARE RESET</li> <li>ENDPOINT RESET</li> </ul>                                                                                                                                                                                                                                                                                            | 29<br>31<br>32<br>32<br>33<br>33                                                                   |

| 5.2<br>5.3<br>6. 1<br>6.1<br>6.2<br>6.3<br>6.4                                                                          | <ul> <li>UFS POWER MODE CONTROL</li> <li>AUTO SLEEP FEATURE</li> <li>RESET OPERATION</li> <li>POWER-ON RESET</li> <li>HARDWARE RESET</li> <li>ENDPOINT RESET</li> <li>LOGICAL UNIT RESET</li> </ul>                                                                                                                                                                                                                                                                       | 29<br>31<br>32<br>32<br>33<br>33<br>33<br>33                                                       |

| 5.2<br>5.3<br><b>6.</b> 1<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5                                                            | <ul> <li>UFS POWER MODE CONTROL</li> <li>AUTO SLEEP FEATURE</li> <li>RESET OPERATION</li> <li>POWER-ON RESET</li> <li>HARDWARE RESET</li> <li>ENDPOINT RESET</li> <li>LOGICAL UNIT RESET</li> <li>UNIPRO RESET</li> </ul>                                                                                                                                                                                                                                                 | 29<br>31<br>32<br>33<br>33<br>33<br>33                                                             |

| 5.2<br>5.3<br>6. 1<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>7. 1                                                           | <ul> <li>UFS POWER MODE CONTROL</li> <li>AUTO SLEEP FEATURE</li> <li>RESET OPERATION</li> <li>POWER-ON RESET</li> <li>HARDWARE RESET</li> <li>ENDPOINT RESET</li> <li>LOGICAL UNIT RESET</li> <li>UNIPRO RESET</li> <li>ENHANCED MEMORY</li> </ul>                                                                                                                                                                                                                        | 29<br>31<br>32<br>33<br>33<br>33<br>33<br>33<br>33                                                 |

| 5.2<br>5.3<br>6. 1<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>7. 1<br>8. 0                                                   | <ul> <li>UFS POWER MODE CONTROL</li> <li>AUTO SLEEP FEATURE</li> <li>RESET OPERATION</li> <li>POWER-ON RESET</li> <li>HARDWARE RESET</li> <li>ENDPOINT RESET</li> <li>LOGICAL UNIT RESET</li> <li>UNIPRO RESET</li> <li>ENHANCED MEMORY</li> <li>COMMAND QUEUING</li> </ul>                                                                                                                                                                                               | 29<br>31<br>32<br>33<br>33<br>33<br>33<br>33<br>33                                                 |

| 5.2<br>5.3<br>6. 1<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>7. 1<br>8. 0<br>9. 7                                           | <ul> <li>UFS POWER MODE CONTROL</li> <li>AUTO SLEEP FEATURE</li> <li>RESET OPERATION</li> <li>POWER-ON RESET</li> <li>HARDWARE RESET</li> <li>ENDPOINT RESET</li> <li>LOGICAL UNIT RESET</li> <li>UNIPRO RESET</li> <li>ENHANCED MEMORY</li> <li>COMMAND QUEUING</li> <li>TASK PRIORITY</li> </ul>                                                                                                                                                                        |                                                                                                    |

| 5.2<br>5.3<br>6. 1<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>7. 1<br>8. 0                                                   | <ul> <li>UFS POWER MODE CONTROL</li> <li>AUTO SLEEP FEATURE</li> <li>RESET OPERATION</li> <li>POWER-ON RESET</li> <li>HARDWARE RESET</li> <li>HARDWARE RESET</li> <li>ENDPOINT RESET</li> <li>LOGICAL UNIT RESET</li> <li>UNIPRO RESET</li> <li>ENHANCED MEMORY</li> <li>COMMAND QUEUING</li> <li>TASK PRIORITY</li> <li>LOGICAL UNIT PRIORITY</li> </ul>                                                                                                                 | 29<br>31<br>32<br>33<br>33<br>33<br>33<br>34<br>35<br>37<br>37                                     |

| 5.2<br>5.3<br>6. 1<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>7. 1<br>8. 0<br>9. 9.1<br>9.2                                  | <ul> <li>UFS POWER MODE CONTROL</li> <li>AUTO SLEEP FEATURE</li> <li>RESET OPERATION</li> <li>POWER-ON RESET</li> <li>HARDWARE RESET</li> <li>ENDPOINT RESET</li> <li>LOGICAL UNIT RESET</li> <li>UNIPRO RESET</li> <li>ENHANCED MEMORY</li> <li>COMMAND QUEUING</li> <li>TASK PRIORITY</li> <li>LOGICAL UNIT PRIORITY</li> </ul>                                                                                                                                         |                                                                                                    |

| 5.2<br>5.3<br>6. 1<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>7. 1<br>8. 0<br>9.<br>9.1<br>9.2<br>10.                        | <ul> <li>UFS POWER MODE CONTROL</li> <li>AUTO SLEEP FEATURE</li> <li>RESET OPERATION</li> <li>POWER-ON RESET</li> <li>HARDWARE RESET</li> <li>ENDPOINT RESET</li> <li>LOGICAL UNIT RESET</li> <li>UNIPRO RESET</li> <li>ENHANCED MEMORY</li> <li>COMMAND QUEUING</li> <li>TASK PRIORITY</li> <li>LOGICAL UNIT PRIORITY</li> <li>COMMAND PRIORITY</li> </ul>                                                                                                               | 29<br>31<br>32<br>32<br>33<br>33<br>33<br>34<br>35<br>37<br>37<br>38<br>38<br>41                   |

| 5.2<br>5.3<br>6. 1<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>7. 1<br>8. 0<br>9. 7<br>9.1<br>9.2<br>10. 10.                  | <ul> <li>UFS POWER MODE CONTROL</li> <li>AUTO SLEEP FEATURE</li> <li><b>RESET OPERATION</b></li> <li>POWER-ON RESET</li> <li>HARDWARE RESET</li> <li>ENDPOINT RESET</li> <li>LOGICAL UNIT RESET</li> <li>UNIPRO RESET</li> <li>ENHANCED MEMORY</li> <li>COMMAND QUEUING</li> <li>LOGICAL UNIT PRIORITY</li> <li>LOGICAL UNIT PRIORITY</li> <li>COMMAND PRIORITY</li> </ul>                                                                                                | 29<br>31<br>32<br>33<br>33<br>33<br>33<br>34<br>35<br>37<br>37<br>37<br>38<br>41<br>41             |

| 5.2<br>5.3<br>6. 1<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>7. 1<br>8. 0<br>9.<br>9.1<br>9.2<br>10. 10.<br>10.             | <ul> <li>UFS POWER MODE CONTROL</li> <li>AUTO SLEEP FEATURE</li> <li>RESET OPERATION</li> <li>POWER-ON RESET</li> <li>HARDWARE RESET</li> <li>ENDPOINT RESET</li> <li>LOGICAL UNIT RESET</li> <li>UNIPRO RESET</li> <li>ENHANCED MEMORY</li> <li>COMMAND QUEUING</li> <li>TASK PRIORITY</li> <li>LOGICAL UNIT PRIORITY</li> <li>COMMAND PRIORITY</li> <li>WRITE PROTECTION</li> <li>1. PERMANENT AND POWER ON WRITE PROTECTION</li> </ul>                                 | 29<br>31<br>32<br>33<br>33<br>33<br>33<br>34<br>35<br>37<br>37<br>38<br>41<br>41<br>42             |

| 5.2<br>5.3<br>6. 1<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>7. 1<br>8. 0<br>9.<br>9.1<br>9.2<br>10. 1<br>10.<br>10.<br>10. | <ul> <li>UFS POWER MODE CONTROL</li> <li>AUTO SLEEP FEATURE</li> <li>RESET OPERATION</li> <li>POWER-ON RESET</li> <li>HARDWARE RESET</li> <li>ENDPOINT RESET</li> <li>LOGICAL UNIT RESET</li> <li>UNIPRO RESET</li> <li>ENHANCED MEMORY</li> <li>COMMAND QUEUING</li> <li>TASK PRIORITY</li> <li>LOGICAL UNIT PRIORITY</li> <li>COMMAND PRIORITY</li> <li>WRITE PROTECTION</li> <li>PERMANENT AND POWER ON WRITE PROTECTION</li> <li>SOFTWARE WRITE PROTECTION</li> </ul> | 29<br>31<br>32<br>33<br>33<br>33<br>33<br>33<br>34<br>35<br>37<br>37<br>38<br>41<br>41<br>42<br>43 |

#### M1PCA00-010

| 11.3.  | WIPE DEVICE                                  |    |

|--------|----------------------------------------------|----|

| 12. RF | MB                                           | 46 |

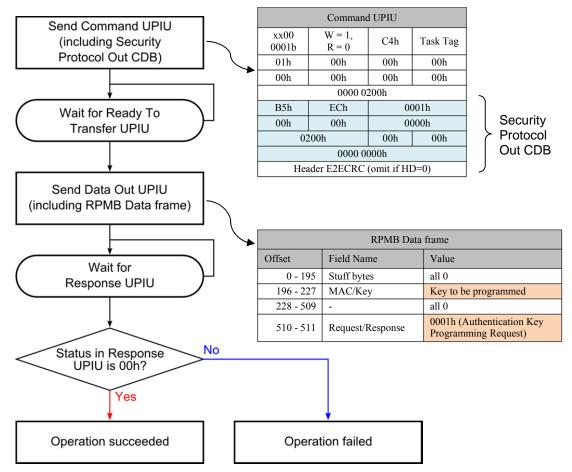

| 12.1.  | AUTHENTICATION KEY PROGRAMMING               | 47 |

| 12.2.  | READ COUNTER VALUE                           |    |

|        | READ/WRITE RPMB DATA                         |    |

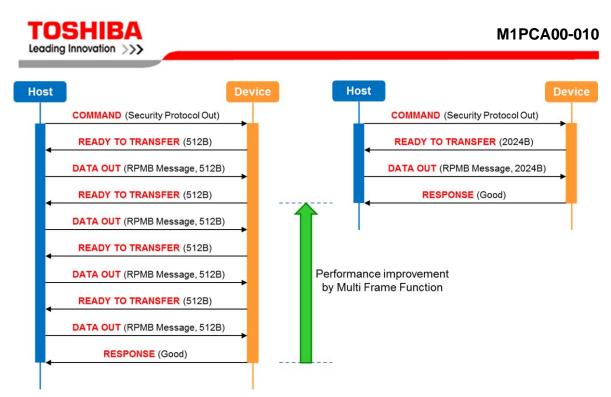

| 12.4.  | RPMB MULTI FRAME FUNCTION (TOSHIBA SPECIFIC) |    |

| 13. CO | NTEXT AND SYSTEM DATA TAG MANAGEMENT         | 55 |

| 14. DA | TA SCRAMBLING                                | 55 |

| DOCU   | MENT REVISION HISTORY                        | 56 |

| RESTR  | ICTIONS ON PRODUCT USE                       | 57 |

# LIST OF TABLES

| Table 1 : Table of Acronyms                                                            | 8   |

|----------------------------------------------------------------------------------------|-----|

| Table 2 : Capacitance Values                                                           | .12 |

| Table 3 : Pin name description                                                         |     |

| Table 4 : Link startup sequence                                                        | .16 |

| Table 5 : Related parameters about power-on sequence                                   | .18 |

| Table 6 : Configuration descriptor format                                              |     |

| Table 7 : Configuration descriptor header and device descriptor configurable parameter | ers |

|                                                                                        | .20 |

| Table 8 : Unit Descriptor configurable parameters                                      |     |

| Table 9 : Parameters related device capacity in Geometry Descriptor                    |     |

| Table 10 : Related parameters about boot operation                                     |     |

| Table 11 : Available state for changing PA_HSSeries                                    |     |

| Table 12 : START_STOP_UNIT command format                                              |     |

| Table 13 : Summary of resets and device behavior                                       |     |

| Table 14 : Summary of resets and device behavior (2)                                   |     |

| Table 15 : Task Management request UPIU format                                         |     |

| Table 16 : Related parameters for Enhanced memory                                      |     |

| Table 17 : Queue depth of LU, Boot W-LU, and RPMB W-LU                                 |     |

| Table 18 : Task Attribute definition                                                   |     |

| Table 19 : Related parameters about write protection                                   |     |

| Table 20 : Control Mode Page format                                                    |     |

| Table 21 : Related parameters about secure removal                                     |     |

| Table 22 : Difference between Erase and Discard operation                              |     |

| Table 23 : Related parameters about Purge operation                                    |     |

| Table 24 : RPMB Message data frame                                                     |     |

| Table 25 : CDB format of Security Protocol In/Out commands                             |     |

| Table 26 : Query Request UPIU and Data Frame Format for Multi Frame Function           |     |

| Table 27 : Query Response UPIU and Data Frame Format for Multi Frame Function          | .53 |

# LIST OF FIGURES

| Figure 1 : UFS Top Level Architecture                                          | 10      |

|--------------------------------------------------------------------------------|---------|

| Figure 2 : UFS System model                                                    | 11      |

| Figure 3 : Block diagram of UFS device                                         |         |

| Figure 4 : Pin connection of BGA package (Top View)                            | 12      |

| Figure 5 : Recommended wiring for TOSHIBA UFS device to a host                 | 14      |

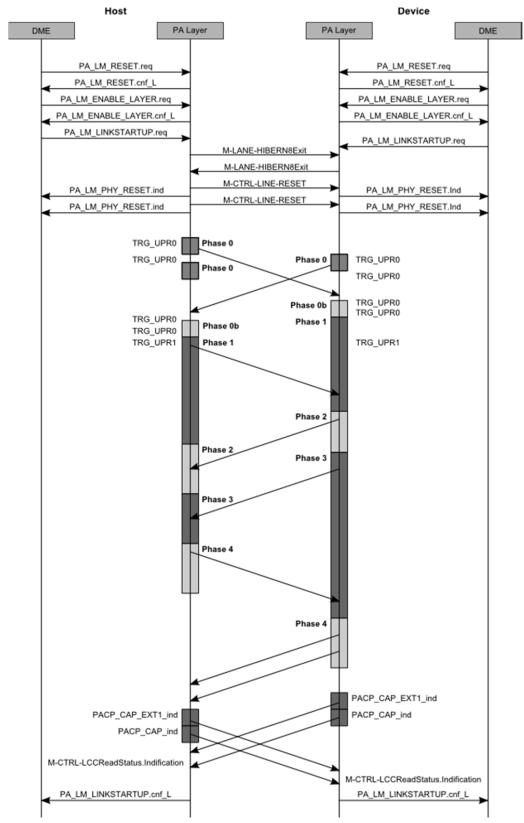

| Figure 6 : Link startup sequence                                               | 17      |

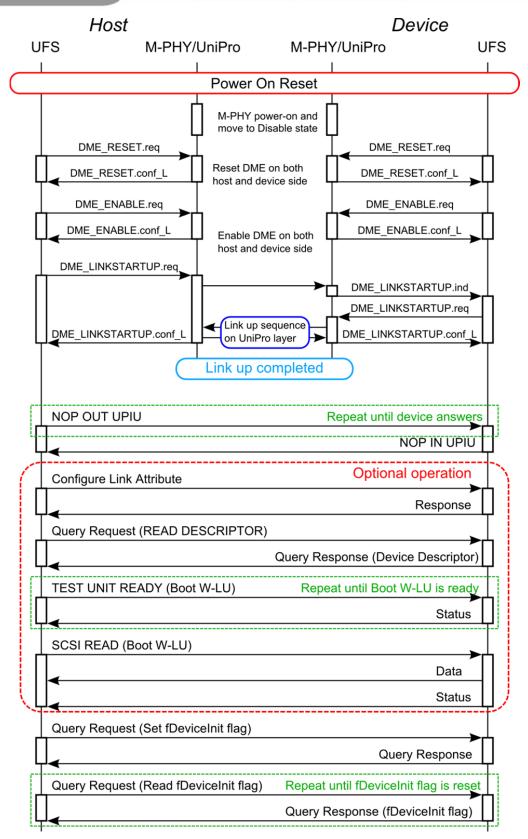

| Figure 7 : Initialization sequence                                             | 19      |

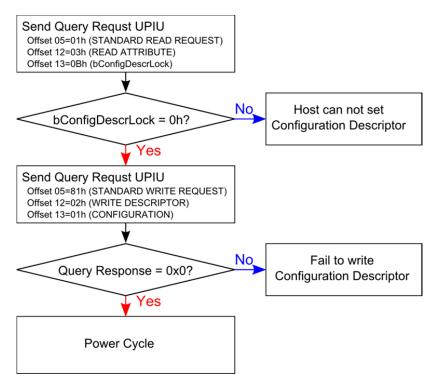

| Figure 8 : Flow chart of writing Configuration Descriptor                      | 22      |

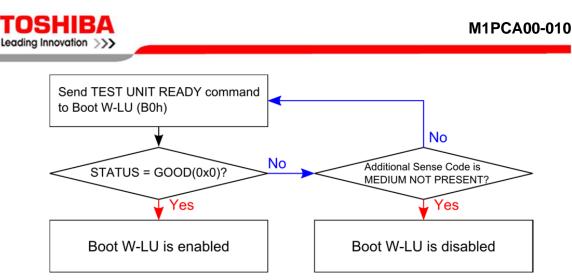

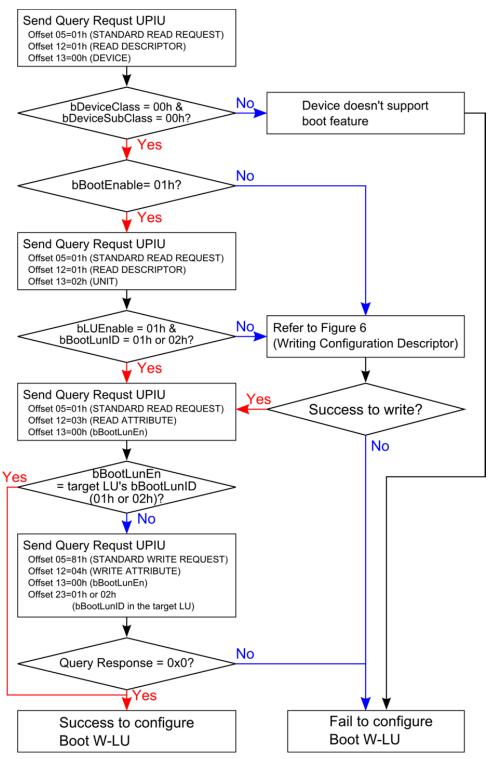

| Figure 9 : Flow chart of checking Boot W-LU                                    | 24      |

| Figure 10 : Flow chart of setting Boot W-LU                                    |         |

| Figure 11 : UniPro power mode change sequence                                  | 28      |

| Figure 12 : Power mode change from Active to Idle                              | 30      |

| Figure 13 : Power mode change from Idle to Active                              | 30      |

| Figure 14 : Power mode change to/from Sleep                                    | 31      |

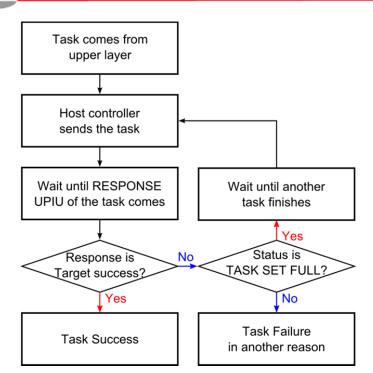

| Figure 15 : Host side handling of task overflow                                | 36      |

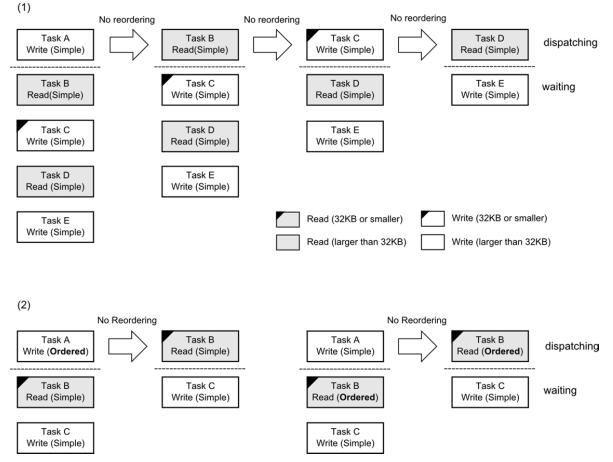

| Figure 16 : Task dispatching order                                             |         |

| Figure 17 : Task dispatching order in a LU                                     | 38      |

| Figure 18 : Task dispatching order in a LU with Ordered attribute task         |         |

| Figure 19 : Example of reordering among tasks with Simple attribute            |         |

| Figure 20 : Example of reordering among tasks with Ordered attribute           | 40      |

| Figure 21 : Flow chart of write protection                                     | 41      |

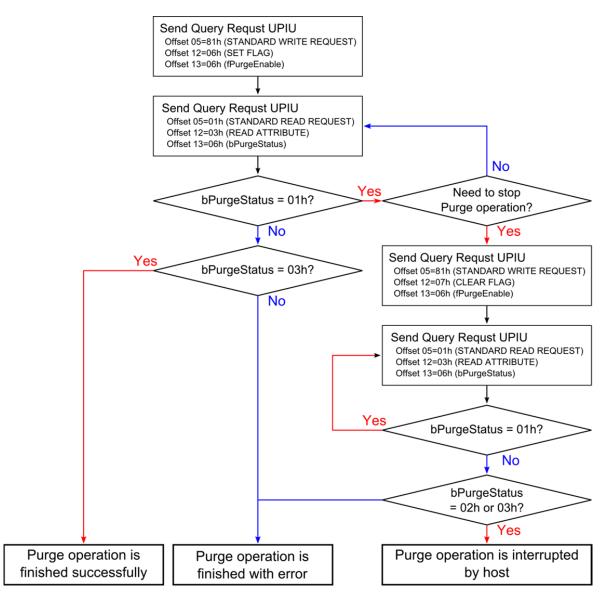

| Figure 22 : Flow chart of Purge operation                                      |         |

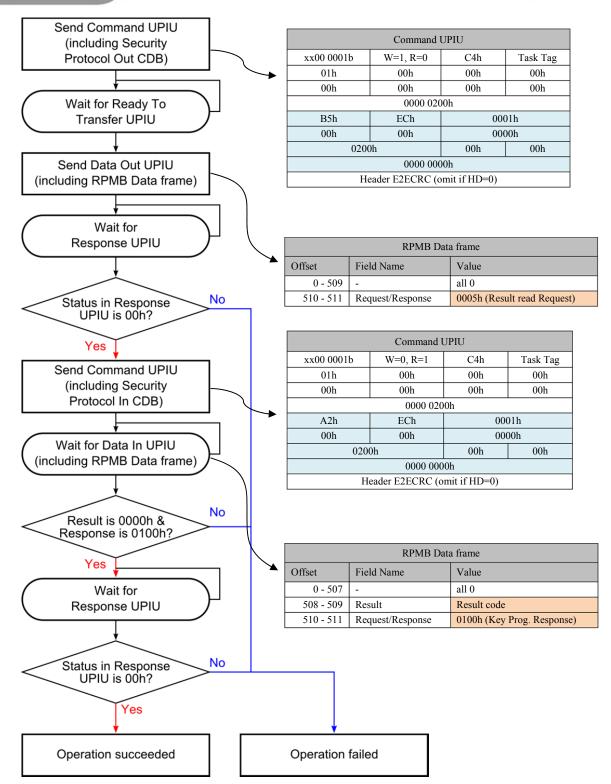

| Figure 23 : Flow chart of Authentication Key programming                       | 47      |

| Figure 24 : Flow chart of Authentication Key programming verification          | 48      |

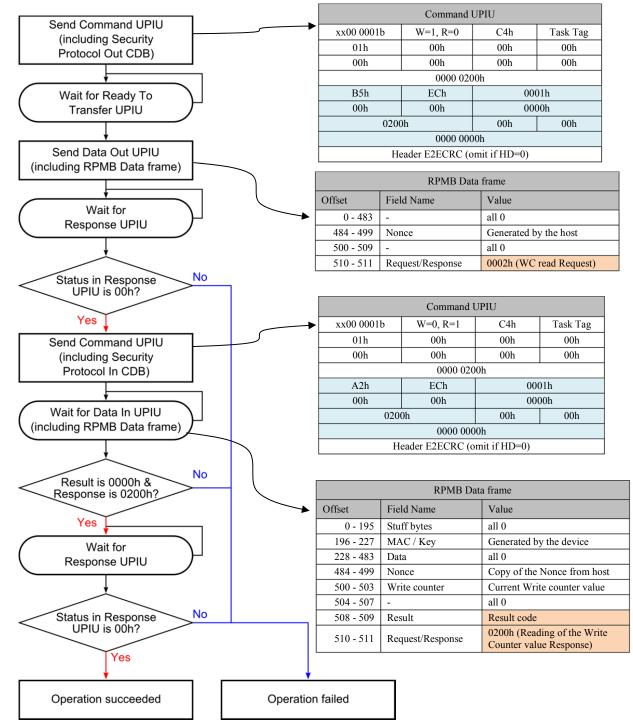

| Figure 25 : Flow chart of read counter value                                   |         |

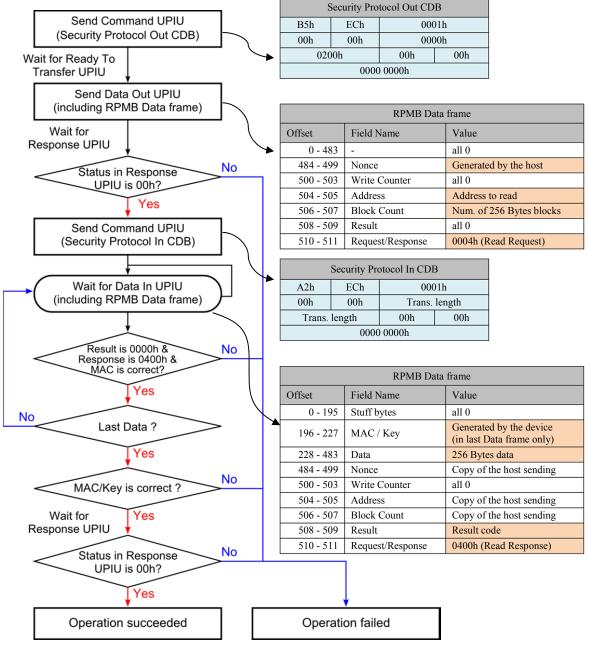

| Figure 26 : Flow chart of Authenticated Read                                   |         |

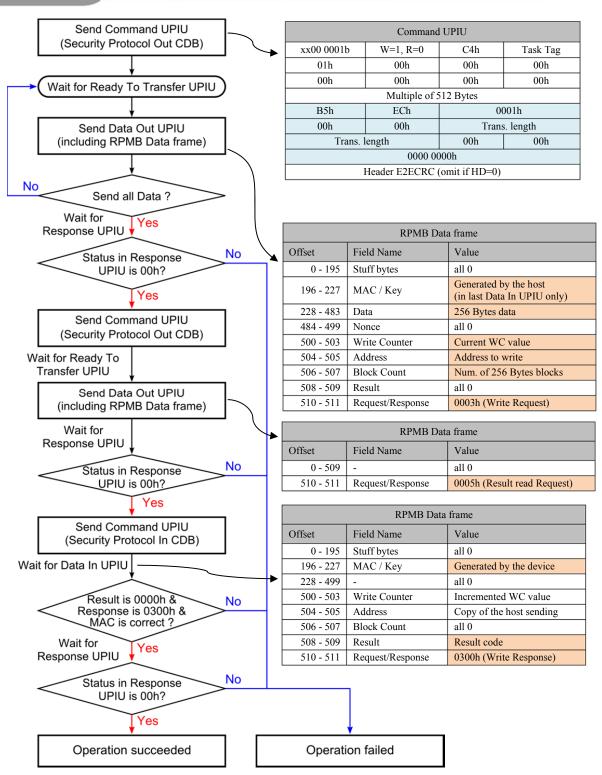

| Figure 27 : Flow chart of Authenticated write                                  |         |

| Figure 28 : Operation image with Multi Frame Function comparing with Single Fi | rame 54 |

# 1. Introduction

## 1.1. Overview

TOSHIBA's UFS memory devies are one of the embedded memory solutions which use nonvolatile NAND flash memory devices for data storage and communication. It consists of NAND flash memory devices and a controller in single Ball Grid Array (BGA) package with the UFS interfaces.

UFS architecture is optimized for mobile devices, thus it has several advantages such as high-performance, low power consumption, low cost, fewer pin count, and small form factor. UFS adopts a protocol stacking structure, which uses MIPI M-PHY<sup>SM</sup> and UniPro<sup>SM</sup> standards for lower layer protocol and SCSI architecture for upper layer protocol. The applications of the UFS cover a wide range of mobile devices such as mobile phones, Slate/Tablet PC, digital video cameras, MP3 player and PNDs, as well as other devices which need embedded memory devices inside.

TOSHIBA's latest UFS is based upon JEDEC UFS standard version 2.0.

# **1.2. Definitions and Acronyms**

#### Table 1 : Table of Acronyms

| Acronyms | Definition                                               |

|----------|----------------------------------------------------------|

| BGA      | Ball Grid Array                                          |

| CDB      | Command Descriptor Block                                 |

| DME      | Device Management Entity                                 |

| HCI      | Host Controller Interface                                |

| LU       | Logical Unit                                             |

| LUN      | Logical Unit Number                                      |

| MIPI     | Mobile Industry Processor Interface                      |

| MLC      | Multi Level Cell                                         |

| NA       | Not applicable                                           |

| PND      | Portable Navigation Device or Personal Navigation Device |

| PWM      | Pulse Width Modulation                                   |

| RFU      | Reserved for future use                                  |

| RPMB     | Replay Protected Memory Block                            |

| SBC      | SCSI Block Commands                                      |

| SPC      | SCSI Primary Commands                                    |

| UFS      | Universal Flash Interface                                |

| UniPro   | Unified Protocol.                                        |

| UPIU     | UFS Protocol Information Unit                            |

| UTP      | UFS Transport Protocol                                   |

| W-LU     | Well known logical unit                                  |

#### **1.3.** Normative reference

This document refers following normative documents. For dated references, subsequent amendments to, or revisions of, any of these publications do not apply. For undated references, the latest edition of the normative document referred to applies.

- [UFS] JEDEC Specification for UFS Version 2.0

- [M-PHY] MIPI Alliance Specification for M-PHY<sup>SM</sup> Version 3.0

- [UniPro] MIPI Alliance Specification for Unified Protocol (UniPro<sup>SM</sup>) Version 1.6

- [SAM] SCSI Architecture Model 5 (SAM-5), Rev. 05, 19 May 2010

- [SPC] T10 Specification: SCSI Primary Commands 4 (SPC-4), Rev.27, 11 October 2010

- [SBC] T10 Specification: SCSI Block Commands 3 (SBC-3), Rev.24, 05 August 2010

# 2. UFS System Architecture

## **2.1. JEDEC UFS standard**

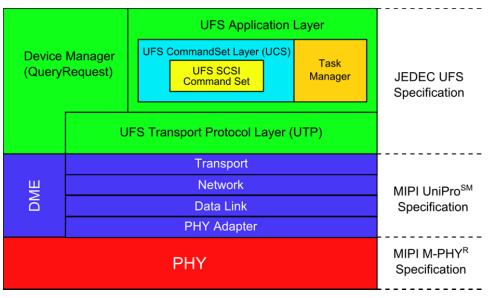

JEDEC UFS standard adopts a protocol stacking structure like OSI reference model. M-PHY<sup>SM</sup> is adopted for physical layer, UniPro<sup>SM</sup> is adopted for data link layer and network layer, transport layer, and UFS defines application layer. Also, UFS adopts Simplified SCSI command set based on SBC and SPC. It can save resources to develop driver software.

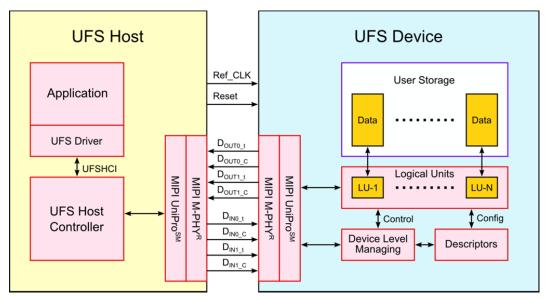

Figure 1 shows UFS top level architecture, and Figure 2 shows UFS System model.

Figure 1 : UFS Top Level Architecture

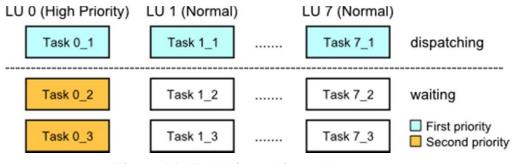

UFS standard defines Logical Unit which has an independent address space. Each LU processes SCSI tasks and performs task management functions independently. The LUs, which have same memory type, have independent address space logically, but physically share same memory space.

Maximum number of LU is 8 in the standard, and TOSHIBA UFS device also supports maximum 8 LUs.

Figure 2 : UFS System model

# 2.2. Block Diagram of UFS device

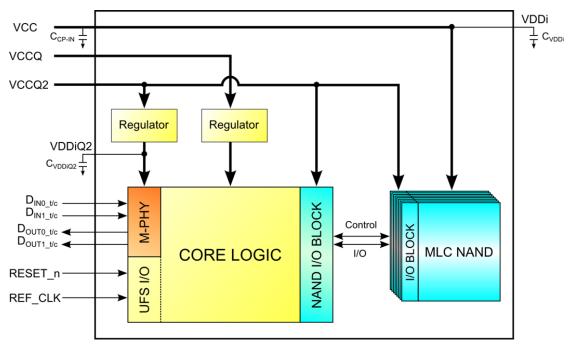

TOSHIBA UFS device consists of raw MLC NAND chip(s) and a controller, which are put in a standard Ball Grid Array (BGA) package. Figure 3 shows an example of the block diagram of the UFS device, and specifications of capacitance in Figure 3 are listed in Table 2.

Figure 3 : Block diagram of UFS device

**Table 2 : Capacitance Values**

| Parameter                          | Symbol              | Min. | Тур | Max. | Unit |

|------------------------------------|---------------------|------|-----|------|------|

| VCCQ2 internal regulator capacitor | C <sub>VDDiQ2</sub> | 0.7  | 2.2 | 2.4  | μF   |

# 2.3. Pin connection of BGA package

The BGA package has 153 balls, and ball layout and pin assignments are compliant with JEDEC UFS standard. Figure 4 shows pin connections of the package of TOSHIBA UFS device.

Table 3 : Pin name description

| Name  | Туре   | Description                                               |  |

|-------|--------|-----------------------------------------------------------|--|

| VCC   | Supply | upply voltage for NAND chips                              |  |

| VCCQ  | Supply | Supply voltage for memory controller                      |  |

| VCCQ2 | Supply | Supply voltage for NAND I/O interface and M-PHY interface |  |

| VDDi  | -      | Shall be connect to VCC or left floating                  |  |

| VDDiQ | -      | Shall be connect to VCCQ or left floating                 |  |

| VDDiQ2    | Input  | Input terminal to provide bypass capacitor for VCCQ2 internal regulator                                |  |

|-----------|--------|--------------------------------------------------------------------------------------------------------|--|

| VSS       | Supply | Ground                                                                                                 |  |

| RESET_N   | Input  | Input hardware reset signal                                                                            |  |

| REF_CLK   | Input  | Input reference clock. When not active, this signal should be pull-down or driven low by the host SoC. |  |

| DIN0/1_t  | Input  | Downstream data lane                                                                                   |  |

| DIN0/1_c  | Input  | Downstream data lane                                                                                   |  |

| DOUT0/1_t | Output | Upstream data lane                                                                                     |  |

| DOUT0/1_c | Output | Upstream data lane                                                                                     |  |

| CPOUT1/2  | -      | No connection. Shall be connected to ground or left floating.                                          |  |

| C+/C-     | -      | No connection. Shall be connected to ground or left floating.                                          |  |

| RFU       | -      | Reserved for Future Use. Shall be connected to ground or left floating.                                |  |

| VSFn      | -      | Shall be left floating                                                                                 |  |

#### **2.4. NC Pins Treatment**

Some of the NC pins are used in TOSHIBA's internal testing. These pins are set to Hi-Z after product shipment and basically there should be no problem even if these pins are connected to GND or other signal line. (In case of connecting to a signal line, increase of capacitance has to be considered.)

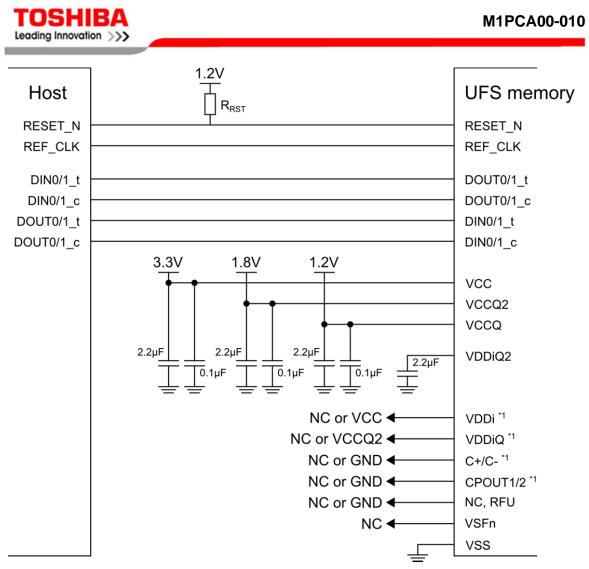

# 2.5. Recommended Wiring: HOST BUS

DINn\_t/c and DOUTn\_t/c are high speed differential signals defined by MIPI M-PHY. These signals operate at maximum 5.8Gbps, therefore users have to pay enough attention for board layout.

DINn\_t/c and DOUTn\_t/c path between a host and a device should be designed for differential  $100\Omega$  (near  $50\Omega \times 2$ ) impedance to have loose coupling, and kept the length as short as possible. Each high speed differential signal pair should be placed  $300\mu$ m far from other signals. TOSHIBA also recommends characterizing transmission lines by electromagnetic simulator.

If some of DINn\_t/c or DOUTn\_t/c are not used, the DINn\_t/c is recommended to be connected to GND and DOUTn\_t/c is recommended to be left floating.

Figure 5 : Recommended wiring for TOSHIBA UFS device to a host

\*1 : VDDi, VDDiQ, C+, C-, CPOUT1, and CPOUT2 pins are not used on TOSHIBA UFS devices.

# 2.6. Recommended Wiring: RESET\_N

Specifications of the hardware reset timings are defined in the datasheet of each product. Users need to arrange the hardware reset wiring so as to satisfy the specifications. The appropriate value of  $R_{RST}$  depends on system design.

# **3.** Initialization sequence

UFS has layer stack architecture and power-on sequence takes place from lowest layer to highest layer.

#### **3.1.** Power supply sequence

TOSHIBA UFS device requires 3 power sources. Users need to satisfy the timing for applying power supplies defined in UFS standard and Technical Documentation of TOSHIBA UFS devices.

#### **3.2.** M-PHY layer initialization

After power-on or HW reset, M-PHY layer is initialized by itself on both host and device side automatically. After finishing M-PHY initialization, the layer is in Hibern8 state.

#### 3.3. UniPro layer initialization

After power-on, HW reset, and DME\_RESET, UniPro layer is in Disable state and is initialized in the following sequence.

- 1. Send DME\_RESET.req primitive

- 2. Wait until DME\_RESER.cnf\_L is received

- 3. Send DME\_ENABLE.req primitive

- 4. Wait until DME\_ENABLE.cnf\_L is received

- 5. Reset attributes to initial values

- 6. Send DME\_LINKSTARTUP.req primitive

- 7. Wait until DME\_LINKSTARTUP.req is received

TOSHIBA UFS devices support link startup initiation on both ends. Link startup is performed in PWM-G1. After link startup sequence is done successfully, the UniPro layer is in Linkup state, and its power mode is set to SlowAuto\_Mode. Please refer to the following sequence for more information.

| Phase | PA Transmitter                                                                    | PA Receiver                                                                                                                               |

|-------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | Continue to send TRG_UPR0 (all lanes)                                             | Wait for TRG_UPR0 reception. Lane discovery                                                                                               |

| 0b    | Send two additional TRG_UPR1                                                      | Ignore all data                                                                                                                           |

| 1     | Continue to send TRG_UPR1                                                         | Wait for TRG_UPR1 reception on all lanes. Re-align Lane numbering                                                                         |

| 2     | Send two additional TRG_UPR1. Then proceed with phase 3.                          | Ignore all data                                                                                                                           |

| 3     | Continue to send TRG_UPR2 on all lanes                                            | Wait for TRG_UPR2 reception on PHY<br>RX Data Lane 0.<br>- TRG_UPR1 (M-PHY: ignored)<br>- Others (M-PHY: ignored)<br>- TRG_UPR2 (Phase 4) |

| 4     | Send two additional TRG_UPR2 on all lanes. Then proceed with Phase 5.             | Ignore all data                                                                                                                           |

| 5     | Transfer Capabilities, Initiate Capability transfer of potential Media Converter. | Receive Capabilities and apply down grading                                                                                               |

| 5     | Report to the DME using PA_LM_LINKS' Sequence succeeded. Exit the Link Startup    | _ 1                                                                                                                                       |

# Table 4 : Link startup sequence

Figure 6 : Link startup sequence

## **3.4. UFS layer initialization**

After UniPro and M-PHY initialization, the following sequence needs to be executed to initialize UFS layer.

- Send NOP OUT UPIU to confirm that a UFS device is ready to receive UPIU.

\* When a device is ready, a single NOP IN UPIU is returned to a host as a response. If a response is not returned, please try to send NOP OUT UPIU from a host again.

- 2. If necessary, do the following optional operation.

- (2-1) Configure the Link Attribute (i.e. Gear, HS Series, PWM Mode in TX and RX)

- (2-2) Read Device Descriptor. (Only when bDescrAccessEn = 01h)

- (2-3) Download the boot code from Boot W-LU. (In case that Boot LU is enable and boot code is already written.)

- 3. Set 01h to fDeviceInit flag, and poll this flag until the device clear it.

After the sequence is done successfully, the UFS layer moves to the state defined by bInitPowerMode in Device Descriptor. At the time of shipment of the device, all logical units except for RPMB well known logical units are disabled. So, users need to configure Unit Descriptors once and activate the setting of the descriptors by a power cycle. Please refer to Section 4.1 for more information.

| Offset   | Size      | Name           | Description                                                                                                                  |

|----------|-----------|----------------|------------------------------------------------------------------------------------------------------------------------------|

| Device D | escriptor |                |                                                                                                                              |

| 09h      | 1         | bDescrAccessEn | 00h: Device Descriptor access disabled<br>01h: Device Descriptor access enabled                                              |

| 0Ah      | 1         | bInitPowerMode | 00h: UFS-Sleep Mode<br>01h: Active Mode                                                                                      |

| Flags    |           |                |                                                                                                                              |

| 01h      | 1         | fDeviceInit    | <ul><li>0b: Device initialization completed or not<br/>started yet.</li><li>1b: Device initialization in progress.</li></ul> |

Table 5 : Related parameters about power-on sequence

After logical unit configuration, a host can access to the configured logical units, but the condition of each logical unit is UNIT ATTENTION as initial condition. If a host issues a command in this condition, a device returns a response of CHECK CONDITION status with the sense key of UNIT ATTENTION. So, it is recommended that REQUEST SENSE command is issued once for each logical unit before accessing them. In this case, the device returns a response with the status of GOOD and clears UNIT ATTENTION condition.

**Figure 7 : Initialization sequence**

SHIBA

Leading Innovation >>>

# 4. Device configuration

UFS standard defines a block of parameters, Descriptor, which specifies the composition of a device. Most of descriptors are read only, but some of them can be configured by users. Basically, these configurable descriptors need to be configured during system design. This chapter provides information on how to configure the descriptors.

#### 4.1. Logical unit configuration

TOSHIBA UFS device supports maximum 8 logical units so that users can configure the memory area of the device according to their usage. Each logical unit has different memory space and it can be used like a partition.

At the time of shipment of the device, all logical units except for RPMB well known logical units are disabled. Therefore users must set following configurable parameters in Device Descriptor and Unit Descriptor before accessing logical units. Configured parameters are valid after a power cycle.

#### **Configurable parameters**

Table 6 shows Configuration Descriptor Format. Configuration parameters consist of Configuration Descriptor header, parameters of Device Descriptor, and parameters of Unit Descriptor.

| Offset               | Description                                                                      |  |

|----------------------|----------------------------------------------------------------------------------|--|

| 00h-0Fh <sup>1</sup> | Configuration Descriptor header and<br>Device Descriptor configurable parameters |  |

| 10h-1Fh <sup>1</sup> | Unit Descriptor 0 configurable parameters                                        |  |

| :                    |                                                                                  |  |

| 80h-8Fh <sup>1</sup> | Unit Descriptor 7 configurable parameters                                        |  |

Table 6 : Configuration descriptor format

Note 1) Offset values depend on bUD0BaseOffset and bUDConfigPLength parameters in Device Descriptor. UFS standard defines both values are 10h.

| Table 7 : Configuration descriptor header and device descriptor |

|-----------------------------------------------------------------|

| configurable parameters                                         |

| Offset | Size | Name            | Valid value |

|--------|------|-----------------|-------------|

| 00h    | 1    | bLength         | 90h (Fixed) |

| 01h    | 1    | bDescriptorType | 01h (Fixed) |

| 02h    | 1    | Reserved        |             |

| 03h    | 1    | bBootEnable     | 00h-01h     |

| 04h     | 1 | bDescrAccessEn      | 00h-01h                                                        |

|---------|---|---------------------|----------------------------------------------------------------|

| 05h     | 1 | bInitPowerMode      | 00h-01h                                                        |

| 06h     | 1 | bHighPriorityLUN    | 00h-07h, 7Fh                                                   |

| 07h     | 1 | bSecureRemovalType  | 00h, 03h <sup>1</sup>                                          |

| 08h     | 1 | bInitActiveICCLevel | 00h-0Fh                                                        |

| 09h     | 2 | wPeriodicRTCUpdate  | Bits [9:0] are valid <sup>2</sup><br>Bits [15:10] are reserved |

| 0Bh-0Fh | 5 | Reserved            | -                                                              |

Note 1) Supported bSecureRemovalType is defined bSupportedSecRTypes (offset: 1Dh) fields in Geometry Descriptor.

Note 2) This value can be configured, but TOSHIBA UFS device doesn't support this feature.

| Offset          | Size | Name                       | Valid value                                                                                           |

|-----------------|------|----------------------------|-------------------------------------------------------------------------------------------------------|

| LUN*10h+0h      | 1    | bLUEnable                  | 00h-01h                                                                                               |

| LUN*10h+1h      | 1    | bBootLunID                 | 00h-02h                                                                                               |

| LUN*10h+2h      | 1    | bLUWriteProtect            | 00h-02h                                                                                               |

| LUN*10h+3h      | 1    | bMemoryType <sup>1,2</sup> | 00h-04h                                                                                               |

| LUN*10h+4h      | 4    | dNumAllocUnits             | 00000000h - 00001D23h<br>00000000h - 00003A42h                                                        |

| LUN*10h+8h      | 1    | bDataReliability           | 00h-01h                                                                                               |

| LUN*10h+9h      | 1    | bLogicalBlockSize          | 0Ch-0Fh                                                                                               |

| LUN*10h+Ah      | 1    | bProvisioningType          | 00h, 02h-03h                                                                                          |

| LUN*10h+Bh      | 2    | wContextCapabilities       | Bits [3:0]: MaxContextID<br>Bits [6:4]:<br>LARGE_UNIT_MAX_MULTI<br>PLIER_M1<br>Bits [15:7]: Reserved. |

| LUN*10h+(Dh-Fh) | 3    | Reserved                   | -                                                                                                     |

Note 1) TOSHIBA recommends Enhanced memory type 2 (04h) for Boot LU.

Note 2) The size of enhanced memory type is up to 8MB.

Configuration Descriptor can be updated until bConfigDescrLock attribute is set. Once bConfigDescrLock is set, write operation to Configuration Descriptor fails.

In the following case a device responds error status.

- Trying to set invalid value

- The LU which has dNumAllocUnit = 0h is enabled (bLUEnable = 01h)

- Two or more LUs have same bBootLunID (A or B)

- The sum of allocation units exceeds Total Device Capacity

- The number of allocation units in each memory type exceeds "dXXXMaxNAllocU" in Geometry Descriptor.

- \* XXX means type of memory

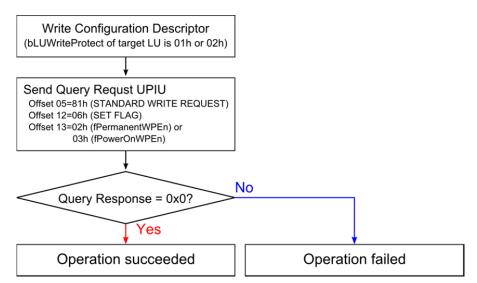

**Figure 8 : Flow chart of writing Configuration Descriptor**

After device configuration is fixed, users are recommended to set bConfigDescrLock (0Bh) attribute. Once bConfigDescrLock is set, Configuration Descriptor is locked and can not be changed.

#### Logical Unit size

The size of a logical unit is defined by dNumAllocUnits. To decide the value of each Logical Unit, users should check parameters of Geometry Descriptor in Table 9 first.

| Offset | Size | Name                    | Description                                                            |

|--------|------|-------------------------|------------------------------------------------------------------------|

| 04h    | 8    | qTotalRawDeviceCapacity | Value expressed in unit of 512 Bytes                                   |

| 0Dh    | 4    | dSegmentSize            | Equivalent to erase block size<br>Value expressed in unit of 512 Bytes |

| 11h    | 1    | bAllocationUnitSize     | Value expressed in number of Segments                                  |

Table 9 : Parameters related device capacity in Geometry Descriptor

Total Device Capacity = qTotalRawDeviceCapacity \* 512[Byte]

Physical Erase Block Size = dSegmentSize \* 512 [Byte]

Allocation Unit Size = bAllocationUnitSize \* (Physical Erase Block Size)

Capacity of a Logical Unit = dNumAllocUnits\* (Allocation Unit Size) / CapAdjFac

\* CapAdjFac = 1 for Normal memory type

In addition, also check the following parameters if memory type is other than Normal memory type. CapAdjFac of each memory type is calculated from the parameters.

- dSystemCodeMaxNAllocU, wSystemCodeCapAdjFac

- dNonPersistMaxNAllocU, wNonPersistCapAdjFac

\* Not supported in TOSHIBA UFS device

- dEnhanced'X'MaxNAllocU, wEnhanced'X'CapAdjFac: 'X' is 1~4

## **Provisioning type**

UFS standard defines 2 provisioning types. One is full provisioning and the other is thin provisioning. TOSHIBA UFS device supports both provisioning types.

When bProvisioningType parameter is set to 00h (full provisioning), all logical block addresses are mapped physically, and UNMAP command is not supported.

When bProvisioningType parameter is set to 02h or 03h (thin provisioning), logical block addresses are mapped or deallocated, and UNMAP command is supported. In case of thin provisioning, the device behavior for UNMAP command is different depending on the value of bProvisioningType. Please refer to Section 11 for more information.

TOSHIBA recommends the use of thin provisioning functionality in the performance point of view.

#### **4.2.** Boot W-LU configuration

2 logical units (Boot LU A, Boot LU B) can be used to store the boot code, but only one of them is active during the boot process. Any logical unit can be configured as "Boot LU A" or "Boot LU B", but 2 or more than logical units can not be assigned to the same Boot LU. The logical unit that is active during boot is mapped onto the Boot well known logical unit (W-LUN = 30h) for read access. Users can confirm whether Boot W-LU is enabled or not by using TEST UNIT READY command.

Figure 9 : Flow chart of checking Boot W-LU

# Enable Boot well known LU

At the time of shipment of the device, Boot W-LU is disabled because all logical units are configured. So, users need to set bBootEnable in Device Descriptor, bBootLunID and bMemoryType in Unit Descriptor, and bBootLunEn attribute to enable boot operation.

TOSHIBA recommends to set Boot well known logical unit as Enhanced memory type 2 (bMemoryType = 04h). The maximum size of enhance memory type 2 is 8MB, so please set the total logical size of Boot well know LU so that it does not exceed 8MB.

| Offset | Size              | Name            | Description                                                                                                                                                                      |  |  |  |  |

|--------|-------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|        | Device Descriptor |                 |                                                                                                                                                                                  |  |  |  |  |

| 03h    | 1                 | bDeviceClass    | 00h: Mass Storage                                                                                                                                                                |  |  |  |  |

| 04h    | 1                 | bDeviceSubClass | 00h: Embedded Bootable                                                                                                                                                           |  |  |  |  |

| 08h    | 1                 | bBootEnable     | 01h: Bootable feature enabled                                                                                                                                                    |  |  |  |  |

|        |                   | Unit Descr      | riptor                                                                                                                                                                           |  |  |  |  |

| 03h    | 1                 | bLUEnable       | 01h: Logical Unit enabled                                                                                                                                                        |  |  |  |  |

| 04h    | 1                 | bBootLunID      | 01h: Boot LU A<br>02h: Boot LU B                                                                                                                                                 |  |  |  |  |

| 08h    | 1                 | bMemoryType     | 00h: Normal Memory<br>01h: System code memory type<br>02h: Non-Persistent memory type<br>03h: Enhanced memory type 1<br>04h: Enhanced memory type 2<br>(recommended for Boot LU) |  |  |  |  |

Table 10 : Related parameters about boot operation

| IDN | Size | Name       | Description                                                          |  |  |

|-----|------|------------|----------------------------------------------------------------------|--|--|

|     |      | Attribut   | e                                                                    |  |  |

| 00h | 1    | bBootLunEn | 01h: Enabled boot from Boot LU A<br>02h: Enabled boot from Boot LU B |  |  |

Figure 10 : Flow chart of setting Boot W-LU

#### **Programming boot code to the device**

Boot W-LU (W-LUN = 30h) is a read-only logical unit, therefore it's prohibited to write data directly. So, a boot code needs to be programmed to a logical unit of which bBootLunID parameter in Unit Descriptor is 01h or 02h. Programmed data to a logical unit which has bBootLunID = 01h or 02h is read through Boot W-LU.

#### **4.3.** Reference clock configuration

TOSHIBA UFS device supports 19.2, 26, 38.4, 52MHz reference clock. The default value is 26MHz. The frequency of reference clock is defined by bRefClkFreq attribute. If a host uses reference clock different from 26MHz, bRefClkFreq should be configured during UFS layer initialization. Please note that bRefClkFreq is write-once attribute.

# 5. Power mode control

UFS standard defines several power modes, and UniPro/M-PHY also defines their own power modes. Both UFS and UniPro/M-PHY power modes are not linked each other, so a host needs to control the power modes independently. The change of power mode in UFS layer is done by issuing SCSI command, while the change of power mode in UniPro layer is done via DME. M-PHY power states are controlled by UniPro depending on UniPro power mode setting, so a host doesn't need to control M-PHY power state directly.

The control of each layer's power mode is important to minimize device power consumption. TOSHIBA UFS device supports all power modes defined in UFS and UniPro standard.

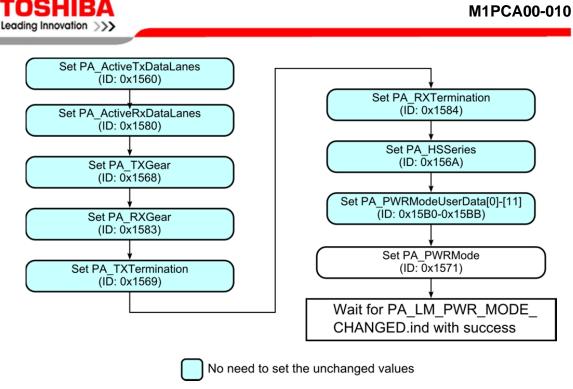

#### **5.1.** UniPro power mode control

UniPro standard defines 6 power modes and a host controls the power modes by attributes and DME requests. UniPro also has "Power States", but these are not configured by a host because the power states automatically change according to the power mode setting.

#### Fast\_Mode, Slow\_Mode, FastAuto\_Mode, and SlowAuto\_Mode

The power mode change between Fast\_Mode, Slow\_Mode, FastAuto\_Mode, and SlowAuto\_Mode is controlled by DME\_POWERMODE or DME\_SET primitive, but DME\_POWERMODE cannot be used because UFS HCI standard.

Setting PA\_PWMMode attribute by DME\_SET triggers UniPro power mode change between Fast\_Mode, Slow\_Mode, FastAuto\_Mode, and SlowAuto\_Mode. So, a host needs to set attributes relative to power mode before setting PA\_PWMMode.

Figure 11 : UniPro power mode change sequence

Please note that TOSHIBA UFS device doesn't support to change PA\_HSSeries during HS-mode operation.

|      |      |     | to  |     |     |     |     |     |     |     |

|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|

|      |      |     |     | PV  | VМ  |     | HS  |     |     |     |

|      |      |     | G1  | G2  | G3  | G4  | G1A | G2A | G1B | G2B |

|      |      | G1  | Yes |

|      | PWM  | G2  | Yes |

|      | PWIN | G3  | Yes |

| from |      | G4  | Yes |

| nom  |      | G1A | Yes | Yes | Yes | Yes | Yes | Yes | No  | No  |

| HS   | US   | G2A | Yes | Yes | Yes | Yes | Yes | Yes | No  | No  |

|      | 115  | G1B | Yes | Yes | Yes | Yes | No  | No  | Yes | Yes |

|      |      | G2B | Yes | Yes | Yes | Yes | No  | No  | Yes | Yes |

Table 11 : Available state for changing PA\_HSSeries

# Hibernate mode

Hibernate enter and hibernate exit procedures are different form normal Power Mode change operation. The power mode of UniPro changes to Hibernate mode by performing DME\_HIBERNATE\_ENTER on a host via HCI. During the transition to Hibernate mode, UniPro changes the Power State of M-PHY to Hibern8 state. UniPro exits from Hibernate mode by DME\_HIBERNATE\_EXIT on a host via HCI.

When entering to Hibernate mode, the current Power Mode configuration including M-PHY settings and lane count information are stored. They are automatically restored when exiting Hibernate mode.

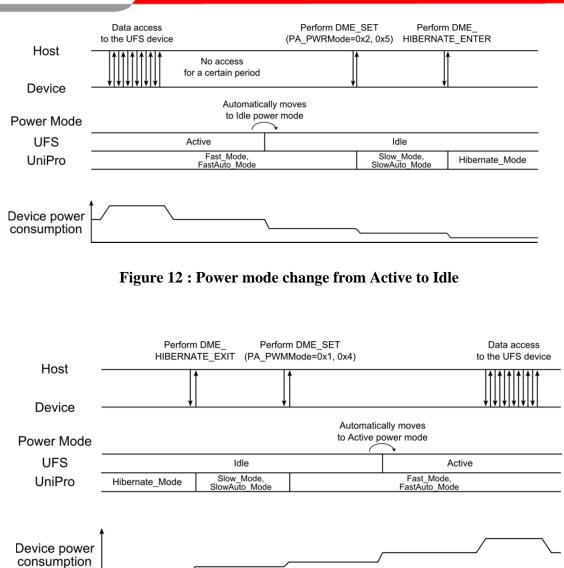

## **5.2. UFS power mode control**

UFS standard defines 4 basic power modes, that is Active, Idle, Sleep, and Power down. These power modes are controlled by POWER CONDITION field in START\_ STOP\_UNIT command and some attributes. To change the device power mode, send the command to UFS Device W-LUN (LUN: D0h). Current power mode can be checked by bCurrentPowerMode Attribute (IDN: 02h).

Also logical units can be stopped individually using this command.

| Bit<br>Byte | 7                                           | 6                 | 5 | 4       | 3         | 2     | 1 | 0     |

|-------------|---------------------------------------------|-------------------|---|---------|-----------|-------|---|-------|

| 0           |                                             |                   | C | PERATIO | N CODE (1 | lBh)  |   |       |

| 1           |                                             | Reserved          |   |         |           |       |   | IMMED |

| 2           |                                             | Reserved          |   |         |           |       |   |       |

| 3           |                                             | Reserved Reserved |   |         |           |       |   |       |

| 4           | POWER CONDITIONResv.NO_<br>FLUSHLOEJ<br>=0b |                   |   |         |           | START |   |       |

| 5           | CONTROL (00h)                               |                   |   |         |           |       |   |       |

Table 12 : START\_STOP\_UNIT command format

Care also NO\_FLUSH field when the device power mode is changed. When the device power mode is changed, all dynamic data including cached data might be lost if NO\_FLUSH field is set (=1b).

#### Active power mode

All operations accessing storage work in this mode. The device moves to this mode via Pre-Active when the device receives START\_STOP\_UNIT command that power condition field is 01h. When a UFS host does not access for a certain period of time, the device moves to Idle power mode automatically.

# Idle power mode

Idle power mode is transited from Active power mode only, and automatically move to Active power mode when the device needs to execute any tasks. To minimize power consumption in this power mode, UniPro power state is recommended to be Hibernate.

Figure 13 : Power mode change from Idle to Active

# **UFS-Sleep power mode**

The power mode moves from Active power mode via Pre-Sleep when the device receives START\_STOP\_UNIT command that power condition field is 02h. In this mode, VCC power supply can be removed.

| Leading Innovation       |                                         |                                                            | M1PCA00-01                                |

|--------------------------|-----------------------------------------|------------------------------------------------------------|-------------------------------------------|

|                          | Send START_<br>STOP_UNIT<br>(PC = 0x02) | Perform DME_ Perform DME_<br>HIBERNATE_ENTER HIBERNATE_EXI | Send START_<br>T STOP_UNIT<br>(PC = 0x01) |

| Host -                   | 1                                       | <b>↑</b>                                                   | 1                                         |

| Device -                 | ¥                                       | ↓                                                          | ↓                                         |

| Power Mode               |                                         |                                                            |                                           |

| UFS                      | Active, Idle                            | Sleep                                                      | Active, Idle                              |

| UniPro                   | Fast_Mode,<br>FastAuto_Mode             | Hibernate                                                  | Fast_Mode,<br>FastAuto_Mode               |

|                          |                                         |                                                            |                                           |

| t                        |                                         |                                                            |                                           |

| Device power consumption |                                         | //                                                         |                                           |

Figure 14 : Power mode change to/from Sleep

## UFS-PowerDown power mode

The power mode moves from Active or Sleep power mode via Pre-PowerDown when the device receives START\_STOP\_UNIT command that power condition field is 03h. All power supplies can be removed. In generally, the device should be entered in this mode before power-off.

# **5.3.** Auto Sleep feature

Auto Sleep is a feature to makes the TOSHIBA UFS device automatically enter into the low power consumption mode when there is no command for a certain period. The period until the TOSHIBA UFS device shifts into the Auto Sleep mode since the last command occurred is defined as auto sleep shift time ( $T_A$ : 10ms).

# 6. Reset operation

TOSHIBA UFS device supports 5 types of reset as follows.

|                    | Valid       | Power mode after r      |                         |              |  |

|--------------------|-------------|-------------------------|-------------------------|--------------|--|

| Reset type         | Power Mode  | bInitPowerMode<br>= 00h | bInitPowerMode<br>= 01h | Boot process |  |

| Power-on reset     | Any         | Pre-Sleep               | Pre-Active              | Enabled      |  |

| Hardware reset     | Any         | Pre-Sleep               | Pre-Active              | Enabled      |  |

| Endpoint reset     | Any         | Pre-Sleep               | Pre-Active              | Enabled      |  |

| Logical Unit reset | Active/Idle | Same as prev.           | Same as prev.           | Disabled     |  |

| UniPro reset       | Any         | Pre-Sleep               | Pre-Active              | Enabled      |  |

#### Table 13 : Summary of resets and device behavior

Table 14 : Summary of resets and device behavior (2)

| Reset Type         | UniPro Stack and<br>Attributes | Volatile and Set<br>Only Attributes<br>and Flags | Power on reset<br>Attributes and<br>Flags | Logical Unit<br>Queue                |

|--------------------|--------------------------------|--------------------------------------------------|-------------------------------------------|--------------------------------------|

| Power-on reset     | Reset                          | Reset                                            | Reset                                     | Reset<br>(all logical units)         |

| Hardware reset     | Reset                          | Reset                                            | Reset                                     | Reset<br>(all logical units)         |

| Endpoint reset     | Reset                          | Reset                                            | Not affected                              | Reset<br>(all logical units)         |

| Logical Unit reset | Not affected                   | Not affected                                     | Not affected                              | Reset<br>(addressed logical<br>unit) |

| UniPro reset       | Reset                          | Reset                                            | No affected                               | Reset<br>(all logical units)         |

#### 6.1. Power-on reset

TOSHIBA UFS device runs Power-on reset operation after switching VCC, VCCQ, or VCCQ2 power supplies off and back on. All Descriptors, Attributes, and Flags are reset and the device processes initialization sequence. VCC power supply can be off when the device is UFS Sleep or PowerDown power mode, and VCCQ and VCCQ2 power supplies can be off when the device is UFS PowerDown power mode. If power supplies are off other than above condition, internal NAND chips might be damaged and automatically perform unexpected shutdown recovery sequence in next power-on sequence.

## 6.2. Hardware Reset

When a RESET\_N pin is set to low for a certain period, the device runs Hardware reset operation. All volatile information including queued tasks is lost after this reset. Hardware reset timing is defined in Technical Documentation of TOSHIBA UFS devices.

## 6.3. Endpoint reset

When the device receives DME\_ENDPOINTRESET from a host, it runs Endpoint reset operation. All volatile information including queued tasks is lost after this reset. This reset is a kind of software reset for the device.

## 6.4. Logical Unit reset

Logical Unit reset is executed by Task Management Request UPIU. To apply this reset, set Task Management Function field in Task Management Request UPIU to 08h (Logical Unit Reset). Only a specified logical unit can be reset and all queued tasks in the logical unit are cancelled. This reset does not affect the device parameters such as attributes and flags.

| Task Management Request UPIU |                   |                             |               |  |  |

|------------------------------|-------------------|-----------------------------|---------------|--|--|

| 0<br>xx00 0100b              | 1<br>Flags        | 2<br>LUN                    | 3<br>Task Tag |  |  |

| 4                            | 5                 | 6                           | 7             |  |  |

| Reserved                     | Task Manag. Func. | Reserved                    | Reserved      |  |  |

| 8                            | 9                 | 10-11                       |               |  |  |

| Total EHS Length             | Reserved          | Data Segment Length (0000h) |               |  |  |

| 12-15                        |                   |                             |               |  |  |

| Input parameter 1            |                   |                             |               |  |  |

|                              |                   |                             |               |  |  |

#### Table 15 : Task Management request UPIU format

# 6.5. UniPro reset

A host can reset its own UniPro layer via the DME\_LINKLOST message. Once the device receives DME\_LINKLOST message from the host, it starts process of re-initializing its own UniPro layer. All UFS level activity has been aborted and all task queue lists are cleared.

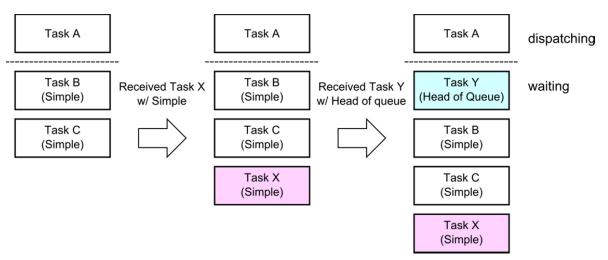

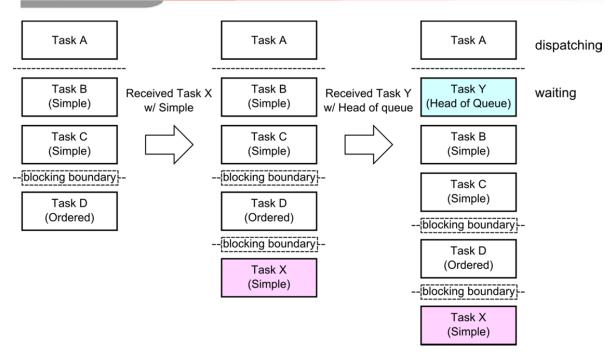

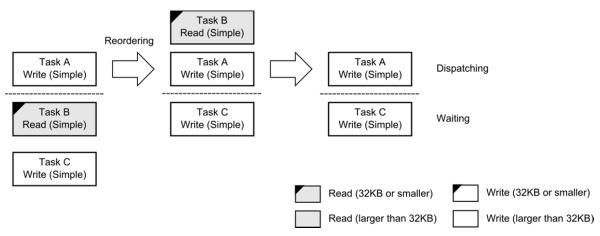

# 7. Enhanced memory